NVIDIA Blogs on Project Denver

![]()

I'm reading this press release as follows,

ARMv8 64-bit Processor.

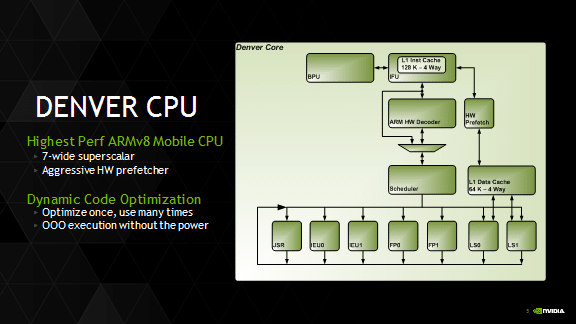

Hardware decode of ARMv8 instructions (see above image).

Seems like similar area: dual core 3-way A16 @ 2.3 GHz -- single core 7-way Denver @ 2.5 GHz.

Run-time "Dynamic Code Optimization" into a 128MB chunk of DRAM backed by a 128KB cache.

7-way looks like (see above image): 2 Load/store units, 2 FPUs, 2 Integer ALUs, 1 Branch unit?

I'm reading this press release as follows,

ARMv8 64-bit Processor.

Hardware decode of ARMv8 instructions (see above image).

Seems like similar area: dual core 3-way A16 @ 2.3 GHz -- single core 7-way Denver @ 2.5 GHz.

Run-time "Dynamic Code Optimization" into a 128MB chunk of DRAM backed by a 128KB cache.

7-way looks like (see above image): 2 Load/store units, 2 FPUs, 2 Integer ALUs, 1 Branch unit?